mirror of

https://github.com/lupyuen/nuttx-sg2000.git

synced 2025-01-12 20:58:29 +08:00

Update doc

This commit is contained in:

parent

b02e4849af

commit

3e124154d1

1 changed files with 30 additions and 4 deletions

34

README.md

34

README.md

|

|

@ -1,4 +1,4 @@

|

|||

|

||||

|

||||

|

||||

[(Watch the Demo on YouTube)](https://www.youtube.com/watch?v=pPNDiC5NLqM)

|

||||

|

||||

|

|

@ -22,11 +22,37 @@ _Why are we doing all this?_

|

|||

|

||||

1. NuttX has been ported from QEMU RISC-V to Star64 JH7110 to Ox64 BL808 and now Sophgo SG2000. Let's find the most efficient way to port NuttX to new RISC-V Devices!

|

||||

|

||||

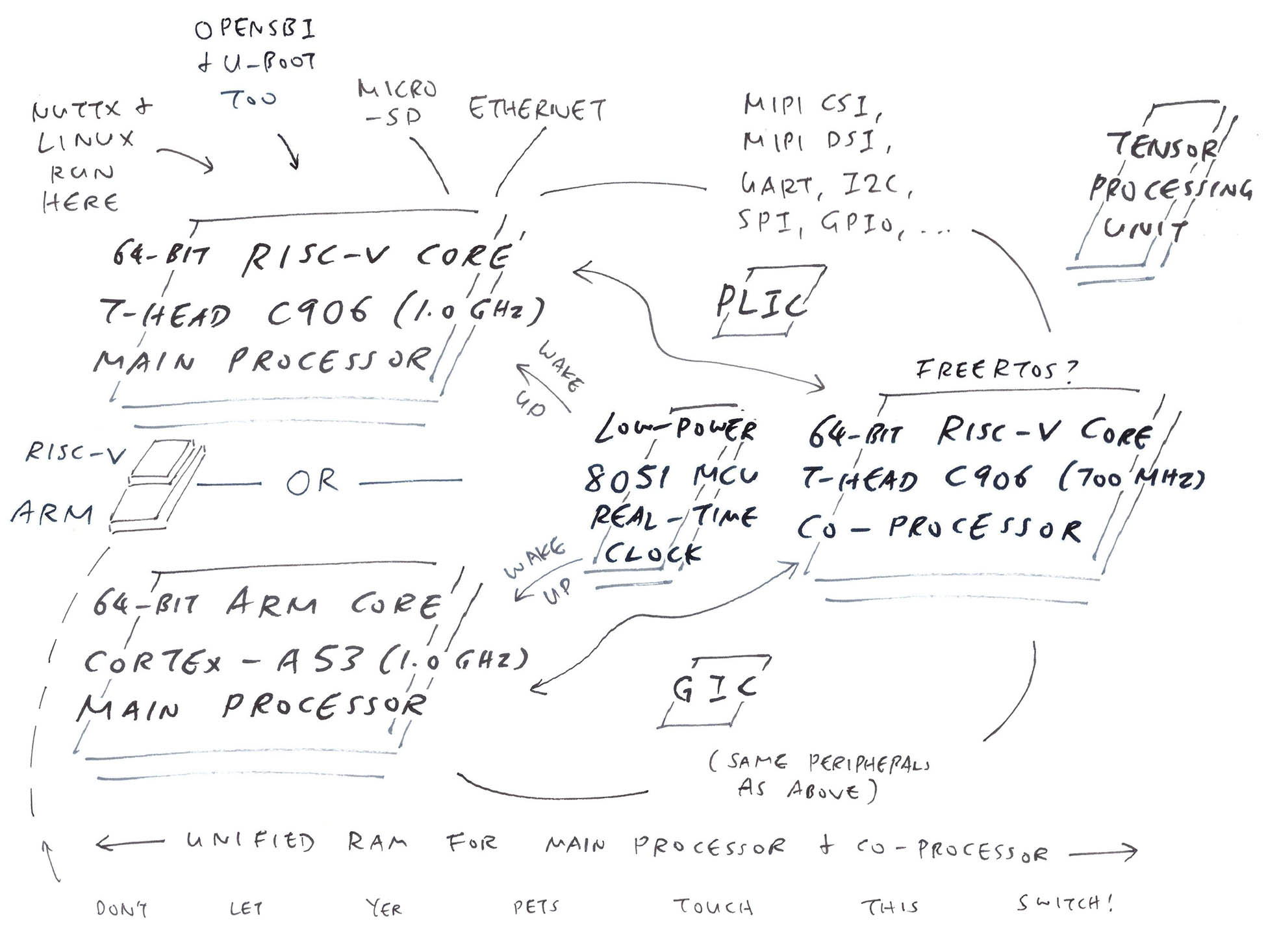

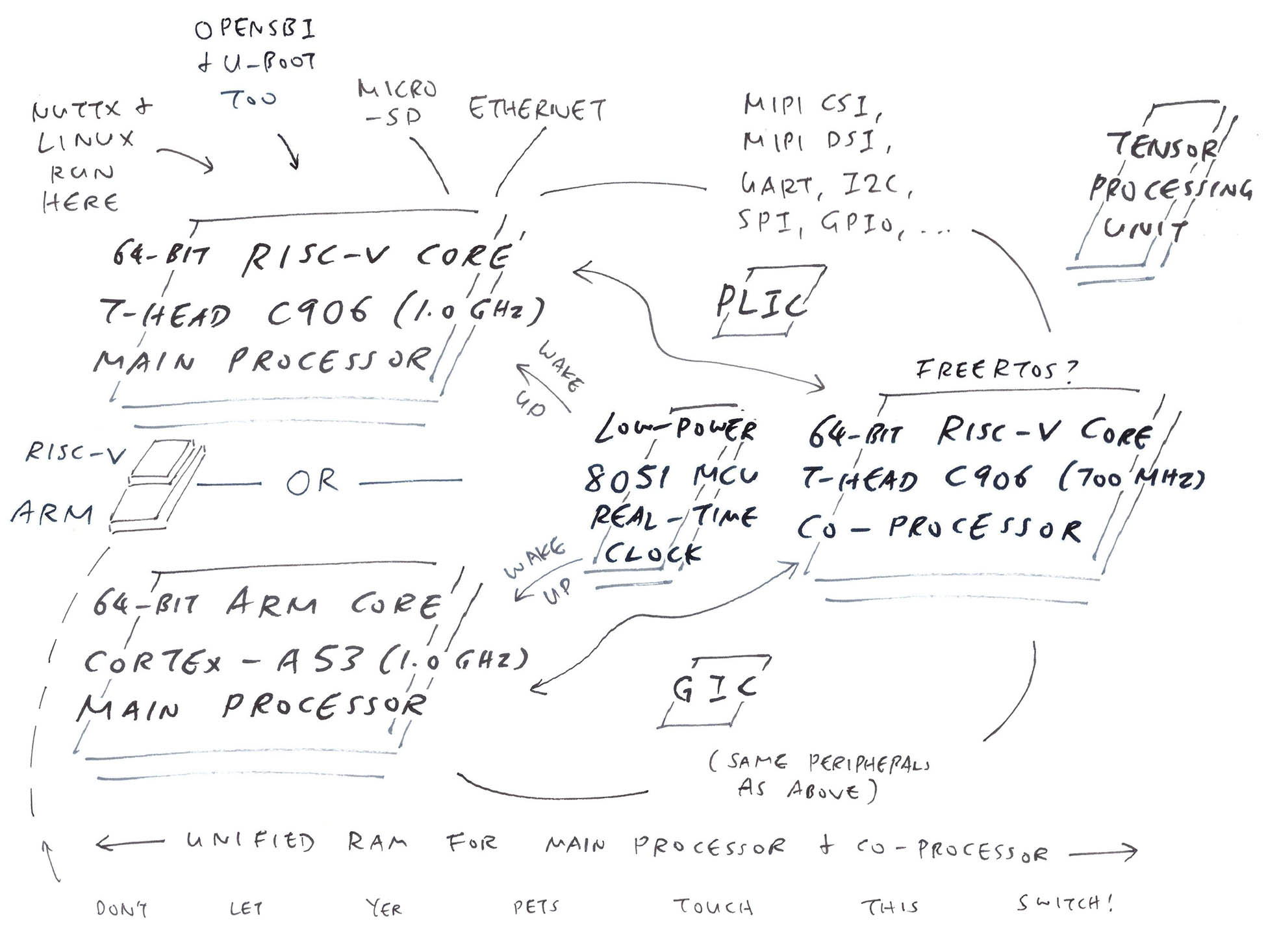

_What's inside Sophgo SG2000 SoC?_

|

||||

|

||||

|

||||

The internals look like this...

|

||||

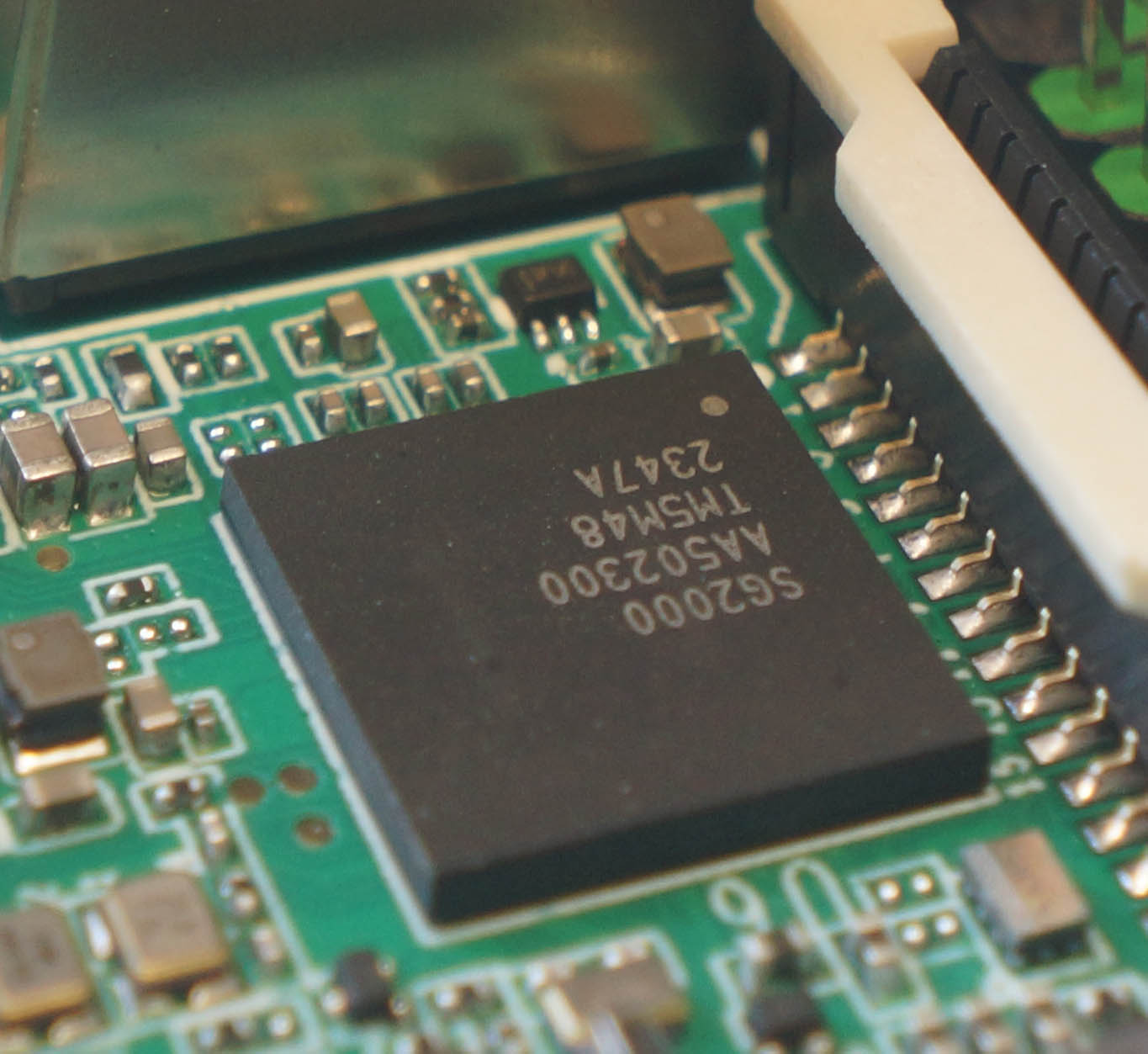

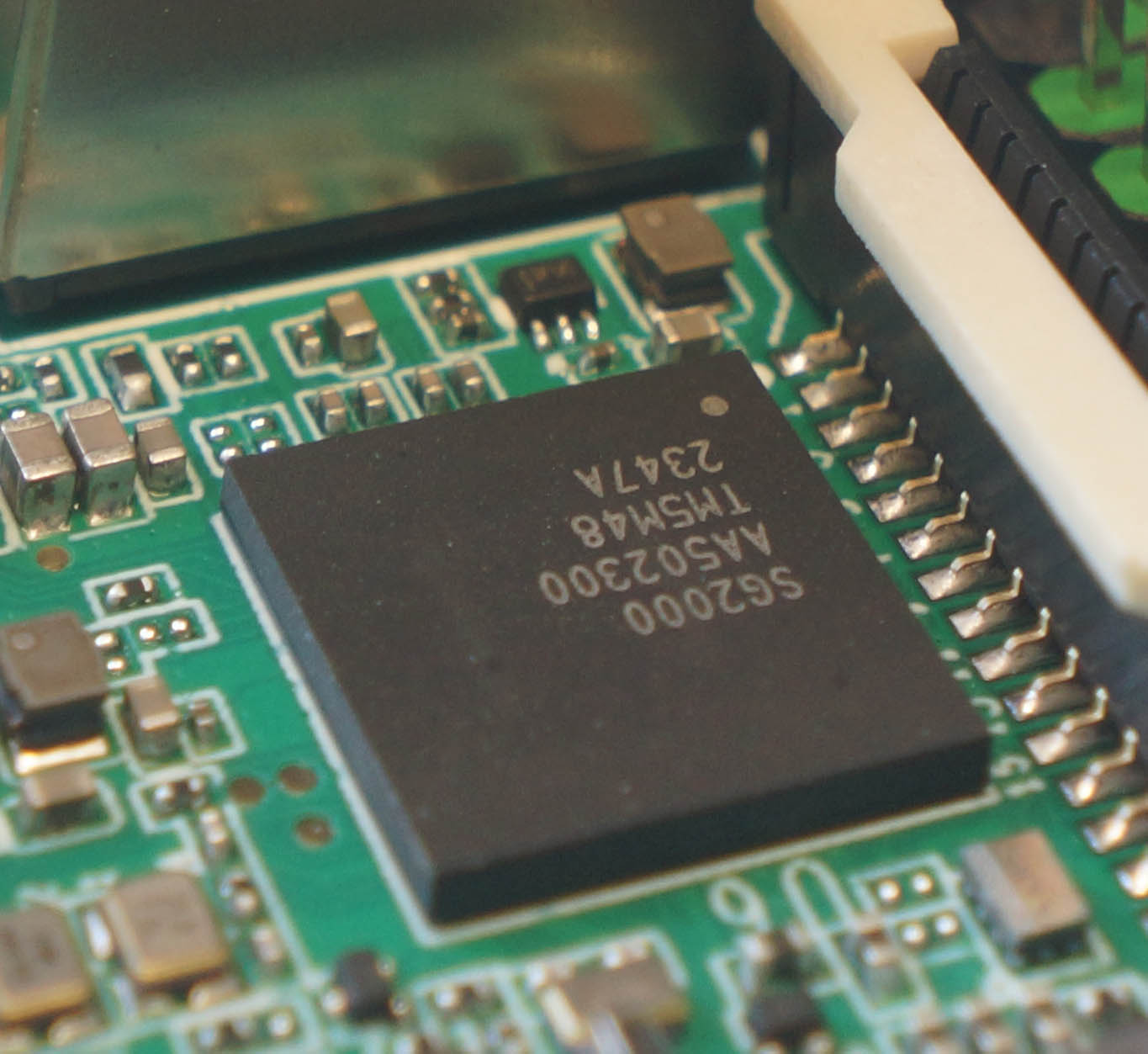

# Sophgo SG2000 RISC-V SoC

|

||||

|

||||

|

||||

__Sophgo SG2000 SoC__ has a fascinating mix of 64-bit RISC-V Cores (Arm too)...

|

||||

|

||||

- __Main Processor:__ 64-bit RISC-V Core

|

||||

|

||||

__T-Head C906__ _(1.0 GHz)_

|

||||

|

||||

(For NuttX and Linux)

|

||||

|

||||

- __Co-Processor:__ 64-bit RISC-V Core

|

||||

|

||||

__T-Head C906__ _(700 MHz)_

|

||||

|

||||

(No Cache)

|

||||

|

||||

- __Alt-Main Processor:__ 64-bit Arm Core

|

||||

|

||||

__Cortex-A53__ _(1.0 GHz)_

|

||||

|

||||

Plus a __Low-Power 8051 MCU__ (for wakeup duties) and a __Tensor Processing Unit__ (for image recognition, not LLM)...

|

||||

|

||||

|

||||

|

||||

_Whoa RISC-V AND Arm CPUs in a single SoC?_

|

||||

|

||||

Actually there's a __Hardware Switch__ that selects the Main CPU: __RISC-V OR Arm__.

|

||||

|

||||

(Don't let yer pet hamster flip it... It will get super frustrating!)

|

||||

|

||||

# Boot Milk-V Duo S without MicroSD

|

||||

|

||||

|

|

|

|||

Loading…

Reference in a new issue